# COLLEGE OF ENGINEERING AND TECHNOLOGIES ALMUSTAQBAL UNIVERSITY

### Electronics CTE 207

Lecture 16

- DC Biasing of BJT - (2023 - 2024)

Dr. Zaidoon AL-Shammari

Lecturer / Researcher

zaidoon.waleed@mustaqbal-college.edu.iq

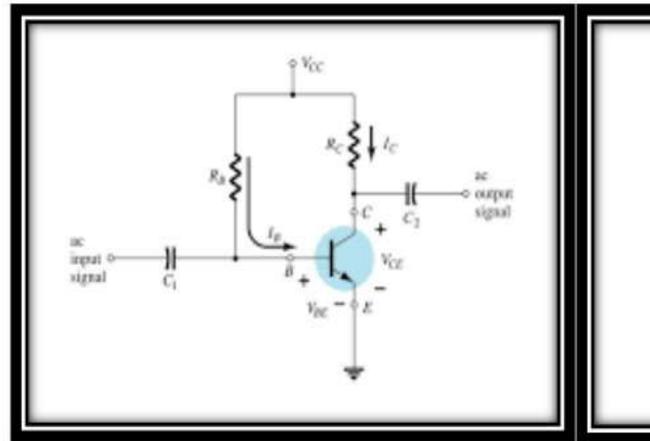

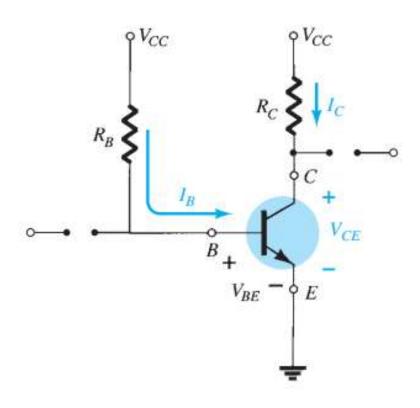

#### Fixed Bias Circuit

The fixed-bias circuit of Figure below provides a relatively straight forward and simple introduction to transistor DC bias analysis.

Even though the network employs an NPN transistor, the equations and calculations apply equally well to a PNP transistor configuration merely by changing all current directions and voltage polarities.

#### Fixed Bias Circuit

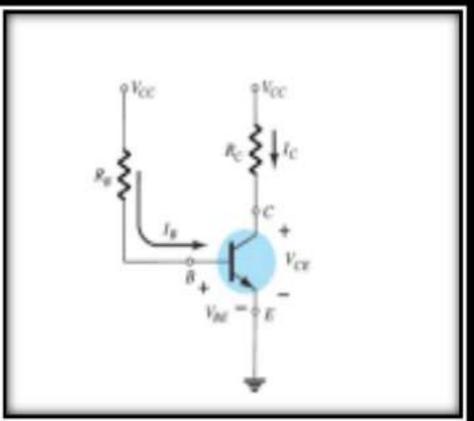

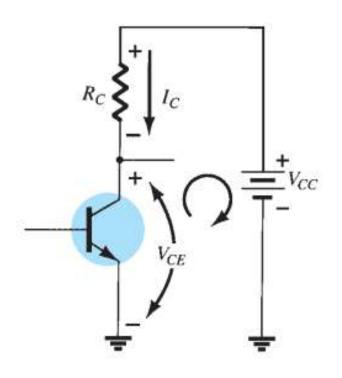

- For the DC analysis the network can be isolated from the indicated AC levels by replacing the capacitors with an open circuit equivalent.

- ➤ In addition, the DC supply VCC can be separated into two supplies (for analysis purposes only) as shown in Figure below.

- The separation is valid, as we note in Figure below that VCC is connected directly to RB and RC just as in Figure below.

### Fixed Bias Circuit

# DC Biasing of BJT

- The analysis or design of a transistor amplifier requires a knowledge of both the DC and AC response of the system.

- The analysis or design of any electronic amplifier therefore has two components: the DC portion and the AC portion.

- Fortunately, the superposition theorem is applicable and the investigation of the DC conditions can be separated from the AC response.

# DC Biasing of BJT

To analysis any network in following these rules are true:

$$V_{BE} \cong 0.7 \text{ V}$$

$$I_E = (\beta + 1)I_B \cong I_C$$

$$I_C = \beta I_B$$

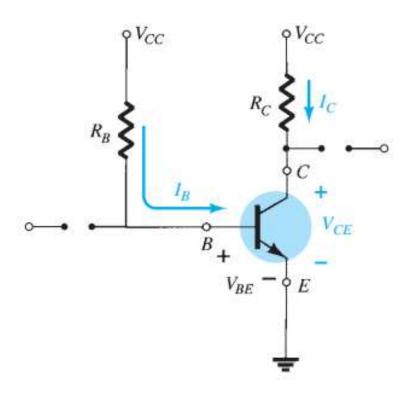

# Base - Emitter loop

## Base - Emitter loop

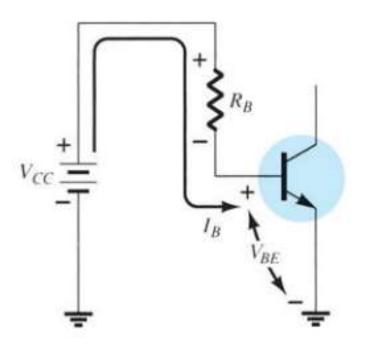

Consider first the base-emitter circuit loop of Fig. 4.4. Writing Kirchhoff's voltage equation in the clockwise direction for the loop, we obtain

$$+V_{CC}-I_BR_B-V_{BE}=0$$

Note the polarity of the voltage drop across  $R_B$  as established by the indicated direction of  $I_B$ . Solving the equation for the current  $I_B$  results in the following:

$$I_B = \frac{V_{CC} - V_{BE}}{R_B}$$

The collector–emitter section of the network appears in Fig. 4.5 with the indicated direction of current  $I_C$  and the resulting polarity across  $R_C$ . The magnitude of the collector current is related directly to  $I_B$  through

$$I_C = \beta I_B$$

It is interesting to note that because the base current is controlled by the level of  $R_B$  and  $I_C$  is related to  $I_B$  by a constant  $\beta$ , the magnitude of  $I_C$  is not a function of the resistance  $R_C$ . Changing  $R_C$  to any level will not affect the level of  $I_B$  or  $I_C$  as long as we remain in the active region of the device. However, as we shall see, the level of  $R_C$  will determine the magnitude of  $V_{CE}$ , which is an important parameter.

Applying Kirchhoff's voltage law in the clockwise direction around the indicated closed loop of Fig. 4.5 results in the following:

$$V_{CE} + I_C R_C - V_{CC} = 0$$

and

$$V_{CE} = V_{CC} - I_C R_C$$

which states that the voltage across the collector–emitter region of a transistor in the fixedbias configuration is the supply voltage less the drop across  $R_C$ .

As a brief review of single- and double-subscript notation recall that

$$V_{CE} = V_C - V_E$$

where  $V_{CE}$  is the voltage from collector to emitter and  $V_C$  and  $V_E$  are the voltages from collector and emitter to ground, respectively. In this case, since  $V_E = 0$  V, we have

$$V_{CE} = V_C$$

In addition, because

$$V_{BE} = V_B - V_E$$

and  $V_E = 0$  V, then

$$V_{BE} = V_B$$

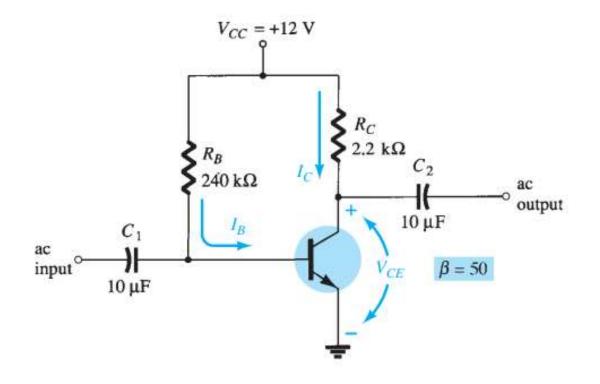

# Example

#### Determine the following for the fixed-bias configuration of Figure below

- a.  $I_{B_Q}$  and  $I_{C_Q}$ . b.  $V_{CE_Q}$ . c.  $V_B$  and  $V_C$ . d.  $V_{BC}$ .

#### Sol

#### Al-Mustaqbal University

a. Eq. (4.4):

$$I_{B_Q} = \frac{V_{CC} - V_{BE}}{R_B} = \frac{12 \text{ V} - 0.7 \text{ V}}{240 \text{ k}\Omega} = 47.08 \,\mu\text{A}$$

Eq. (4.5):  $I_{C_Q} = \beta I_{BQ} = (50)(47.08 \,\mu\text{A}) = 2.35 \,\text{mA}$

b. Eq. (4.6):

$$V_{CE_Q} = V_{CC} - I_C R_C$$

= 12 V - (2.35 mA)(2.2 k $\Omega$ )

= **6.83** V

c.

$$V_B = V_{BE} = 0.7 \text{ V}$$

$V_C = V_{CE} = 6.83 \text{ V}$

d. Using double-subscript notation yields

$$V_{BC} = V_B - V_C = 0.7 \text{ V} - 6.83 \text{ V}$$

= -6.13 V

# AL- MUSTAQBAL UNIVERSITY COMPUTER TECHNIQUES ENGINEERING