Lecturer: Dr. Ameer Al-khaykan

**Lecture: DC Biasing Circuits of BJTs**

## **Basic Concepts:**

The analysis or design of a transistor amplifier requires a knowledge of both the dc and ac response of the system. Too often it is assumed that the transistor is a magical device that can raise the level of the applied ac input without the assistance of an external energy source. In actuality, the improved output ac power level is the result of atransfer of energy from the applied dc supplies. The analysis or design of any electronicamplifier therefore has two components: the dc portion and the ac portion. Fortunately, the superposition theorem is applicable, and the investigation of the dc conditions can et al., and the investigation of the dc conditions can be totally separated from the ac response. However, one must keep in mind that during the design or synthesis stage the choice of parameters for the required dc levels will affect the ac response, and vice versa.

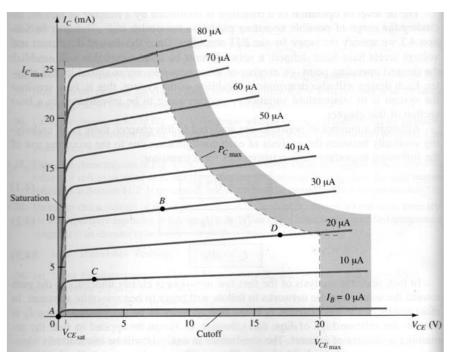

The term *biasing* appearing in the title of this lecture is an all-inclusive term for the application of dc voltages to establish a fixed level of current and voltage. For transistor amplifiers the resulting dc current and voltage establish an *operating point* on the characteristics that define the region that will be employed for amplification of the applied signal. Since the operating point is a fixed point on the characteristics, it is also called the *quiescent point* (abbreviated Q-point). By definition, *quiescent* means quiet, still, inactive. Fig. 9-1 shows a general output device characteristic with four operating points indicated. The biasing circuit can be designed to set the device operation at any of these points or others within the *active region*. The maximum ratings are indicated on the characteristics of Fig. 9-1 by a horizontal line for the maximum collector current  $I_{Cmax}$  and a vertical line at the maximum collector-to-emitter voltage  $V_{CEmax}$ . The maximum power constraint is defined by the curve  $P_{Cmax}$  in the same figure. At the lower end of the scales are the *cutoff region*, defined by  $I_B \leq 0$   $\mu$ A, and the *saturation region*, defined by  $V_{CE} \leq V_{CE(sat)}$ .

Fig. 1

# **Standard Biasing Circuits:**

## 1. Fixed-Bias Circuit:

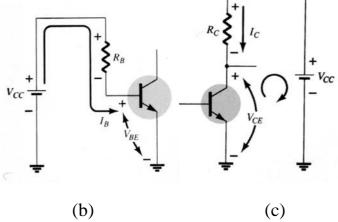

Fig. 9-2a shows a fixed-bias circuit.

### Analysis:

▼ For the input (base-emitter circuit) loop as shown in Fig. 9-2b:

▼ For the output (collector-emitter circuit) loop as shown in Fig. 9-2c:

$$+V_{CE} + I_{C}R_{C} - V_{CC} = 0$$

$$V_{CE} = V_{CC} - I_{C}R_{C}$$

[9.1b]

■ For the transistor terminal voltages:

$$V_E = 0V$$

$$V_B = V_{CC} - I_B R_B = V_{BE}$$

[9.1c]

(a)

Fig. 9-2

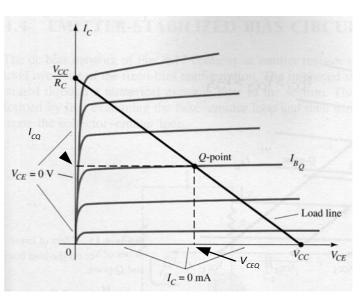

## Load-Line Analysis:

$I_C = \beta I_B$

From Eq. [9.1b] and Fig. 9-3:

■ At cutoff region:

$$\left|V_{CE} = V_{CC}\right|_{I_C = 0}$$

[9.2a]

★ At saturation region:

$$I_C = \frac{V_{CC}}{R_C}\Big|_{V_{CE}=0}$$

[9.2b]

## Design:

For an optimum design:

$$V_{CEQ} = \frac{1}{2}V_{CC}$$

$$I_{CQ} = \frac{1}{2}I_{C(sat)} = \frac{V_{CC}}{2R_{C}}$$

[9-3]

Fig. 9-3

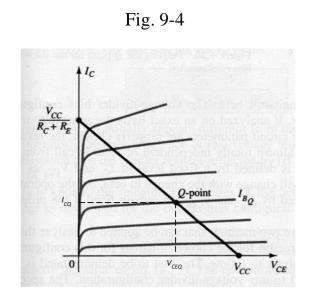

# 2. Emitter-Stabilized Bias Circuit:

Fig. 9-4a shows an emitter-stabilized bias circuit.

### Analysis:

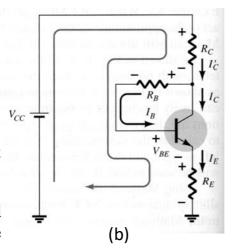

◆ For the input (base-emitter circuit) loop as shown in Fig. 9-4b:

$$+V_{CC}-I_BR_B-V_{BE}-I_ER_E=0$$

$$I_{E} = (\beta + 1)I_{B}$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B} + (\beta + 1)R_{E}}$$

[9.4a]

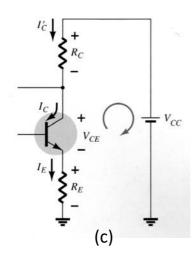

▼ For the output (collector-emitter circuit) loop as shown in Fig. 9-4c:

$$+ I_E R_E + V_{CE} + I_C R_C - V_{CC} = 0$$

$$I_E \cong I_C$$

$$V_{CE} = V_{CC} - I_C (R_C + R_E)$$

[9.4b]

■ For the transistor terminal voltages:

$$V_E = I_E R_E$$

$$V_B = V_{CC} - I_B R_B = V_E + V_{BE}$$

[9.4c]

(a)

## Load-Line Analysis:

From Eq. [9.4b] and Fig. 9-5:

◆ At cutoff region:

$$\begin{vmatrix} V_{CE} = V_{CC} |_{I_C=0} \end{vmatrix}$$

[9.5a]

■ At saturation region:

$$I_C = \frac{V_{CC}}{R_C + R_E} \Big|_{V_{CE} = 0}$$

[9.5b]

[9-6]

# 3. Voltage-Divider Bias Circuit:

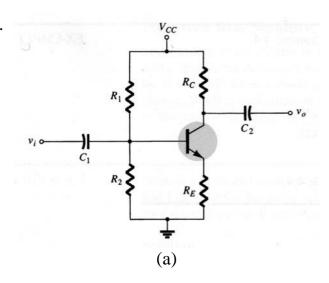

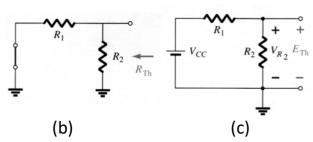

Fig. 9-6a shows a voltage-divider bias circuit.

## Analyses:

◀ For the input (base-emitter circuit) loop:

Exact Analysis:

From Fig. 9-6b:

$$R_{Th} = R_1 R_2$$

[9.7a]

From Fig. 9-6c:

$$E_{Th} = V_{R_2} = \frac{R_2 V_{CC}}{R_1 + R_2}$$

[9.7b]

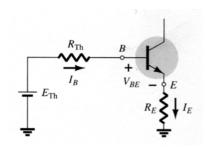

From Fig. 9-6d:

$$+E_{Th}-I_BR_{Th}-V_{BE}-I_ER_E=0$$

$$I_E = (\beta + 1)I_E$$

$$I_{E} = (\beta + 1)I_{B}$$

$$I_{B} = \frac{E_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_{E}}$$

[9.7c]

$$I_C = \beta I_B$$

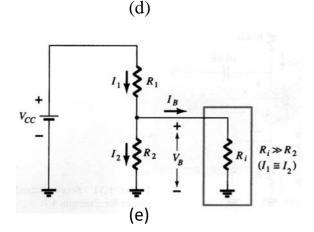

### Approximate Analysis:

From Fig. 9-6e:

If

$$R_i >> R_2 \Rightarrow I_2 >> I_B$$

.

Since

$$I_B \approx 0 \implies I_1 \cong I_2$$

.

Thus  $R_1$  in series with  $R_2$ .

That is

$$V_{B} = \frac{R_{2}V_{CC}}{R_{1} + R_{2}}$$

Since  $\frac{R_{1} + R_{2}}{R_{i} = (\beta + 1)R_{E}} \cong \beta R_{E}$  the condition

that will define whether the approximation approach can be applied will be the following:

$$\beta R_E \ge 10R_2$$

[9.8b] and

$$\begin{vmatrix} V_E = V_B - V_{BE} \\ I_C \cong I_E = \frac{V_E}{R_E} \end{vmatrix}$$

[9.8c]

■ For the output (collector-emitter circuit) loop: Fig. 9-6  $V_{CF} = V_{CC} - I_C (R_C + R_F)$  [9.9]

## Load-Line Analysis:

The similarities with the output circuit of the emitter-biased configuration result in the same intersections for the load line of the voltage-divider configuration. The load line will therefore have the same appearance as that of Fig. 9-5. The level of  $I_B$  is of course determined by a different equation for the voltage-divider bias and the emitter-bias configuration.

## Design:

For an optimum design:

$$V_{CEQ} = \frac{1}{2}V_{CC}$$

$$I_{CQ} = \frac{1}{2}I_{C(sat)} = \frac{V_{CC}}{2(R_C + R_E)}$$

$$V_E = \frac{1}{10}V_{CC}$$

$$R_2 \le \frac{1}{10}\beta R_E$$

[9.10]

## **Example 9-1:**

Determine the dc bias voltage  $V_{CE}$  and the current  $I_C$  for the voltage-divider configuration of Fig. 9-6a with the following parameters:  $V_{CC} = +22$  V,  $\beta = 140, R_I = 39$  k $\Omega$ ,  $R_C = 10$  k $\Omega$ , and  $R_E = 1.5$  k $\Omega$ .

#### **Solution:**

$$R_{Th} = R_1 R_2 = 39k 3.9k = 3.55\Omega$$

$$E_{Th} = \frac{R_2 V_{CC}}{R_1 + R_2} = \frac{(3.9k)(22)}{39k + 3.9k} = 2V$$

$$I_B = \frac{E_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_E}$$

$$= \frac{2 - 0.7}{3.55k + (141)(1.5k)} = 6.05\mu A$$

$$I_{CQ} = \beta I_B = (140)(6.05\mu) = 0.85mA$$

$$V_{CEQ} = V_{CC} - I_C (R_C + R_E)$$

$$= 22 - (0.85m)(10k + 1.5k)$$

$$= 12.23V$$

## Approximate:

Testing:

$$\beta R_E \ge 10R_2$$

$(140)(1.5k) \ge 10(3.9k)$

$210k\Omega > 39k\Omega$  (satisfied)

$V_B = \frac{R_2 V_{CC}}{R_1 + R_2} = \frac{(3.9k)(22)}{39k + 3.9k} = 2V$

$V_E = V_B - V_{BE} = 2 - 0.7 = 1.3V$

$I_{CQ} = I_E = \frac{V_E}{R_E} = \frac{1.3}{1.5k} = 0.867mA$

$V_{CEQ} = V_{CC} - I_C (R_C + R_E)$

$= 22 - (0.867m)(10k + 1.5k)$

$= 12.03V$

# 4. Voltage-Feedback Bias Circuit:

Fig. 9-7a shows a voltage-feedback bias circuit.

### Analysis:

◆ For the input (base-emitter circuit) loop as shown in Fig. 9-7b:

$$+V_{CC} - I'_{C}R_{C} - I_{B}R_{B} - V_{BE} - I_{E}R_{E} = 0$$

$I'_{C} = I_{C} + I_{B} = I_{E} \cong I_{C} = \beta I_{B}$

$$+ V_{CC} - \beta I_B R_C - I_B R_B - V_{BE} - \beta I_B R_E = 0$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B} + \beta (R_{C} + R_{E})}$$

[9.11a]

■ For the output (collector-emitter circuit) loop as shown in Fig. 9-7c:

$$+ I_E R_E + V_{CE} + I'_C R_C - V_{CC} = 0$$

$$I'_C = I_E \cong I_C$$

$$V_{CE} = V_{CC} - I_C (R_C + R_E)$$

[9.11b]

Continuing with the approximation  $I'_{C} = I_{C}$  will result

in the same load line defined for the voltage-divider and emitter-biased configurations. The levels of  $I_{BQ}$  will be defined by the chosen base configuration.

(a)

#### Design:

For an optimum design:

$$V_{CEQ} = \frac{1}{2}V_{CC}$$

$$I_{CQ} = \frac{1}{2}I_{C(sat)} = \frac{V_{CC}}{2(R_C + R_E)}$$

$$V_E = \frac{1}{10}V_{CC}$$

$$R_B \le \beta (R_C + R_E)$$

Fig. 9-7

# **Other Biasing Circuits:**

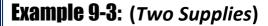

# **Example 9-2**: (Negative Supply)

Determine  $V_C$  and  $V_B$  for the circuit of Fig. 9-8.

#### Solution:

$$-I_B R_B - V_{BE} + V_{EE} = 0$$

(KVL)

$$I_B = \frac{V_{EE} - V_{BE}}{R} = \frac{9 - 0.7}{8} = 83 \mu A 100 k$$

$$I_C = \beta I_B = (45)(83\mu) = 3.735 mA$$

$V_C = -I_C R_C = -(3.735 m)(1.2 k) = -4.48 V$

$V_B = -I_B R_B = -(83\mu)(100 k) = -8.3 V$

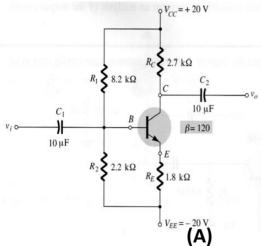

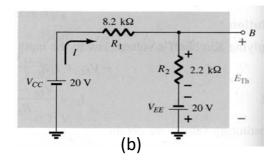

Determine  $V_C$  and  $V_B$  for the circuit of Fig. 9-9a.

#### Solution:

$$R_{Th} = R_1 \parallel R_2 = 8.2k \parallel 2.2k = 1.73k\Omega$$

$$I = \frac{V_{CC} + V_{EE}}{R_1 + R_2} = \frac{20 + 20}{8.2k + 2.2k} = 3.85mA$$

$$E_{Th} = IR_2 - V_{EE} = (3.85m)(2.2k) - 20 = -11.53V$$

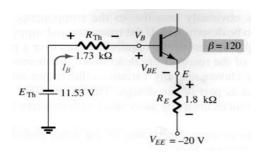

From Fig. 9-9c:

$$-E_{Th} - I_B R_{Th} - V_{BE} - I_E R_{E+} V_{EE} = 0$$

(KVL)

$$I_{E} = (\beta + 1)I_{B}$$

$$I_{B} = \frac{V_{EE} - E_{Th} - V_{BE}}{R_{Th} + (\beta + 1)R_{E}}$$

(C) figure 9-9

$$=\frac{20-11.53-0.7}{1.73k+(121)(1.8k)}=35.39\mu A$$

$$I_C = \beta I_B = (120)(35.39 \mu) = 4.25 mA$$

$$V_C = V_{CC} - I_C R_C = 20 - (4.25m)(2.7k) = 8.53V$$

$$V_B = -E_{Th} - I_B R_{Th} = -(11.53) - (35.39 \mu)(1.73 k) = -11.59 V$$

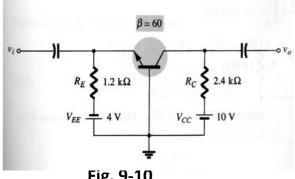

# **Example 9-4**: (Common-Base)

Determine  $V_{CB}$  and  $I_B$  for the common-base configuration of Fig. 9-10.

Solution:

Applying KVL to the input circuit:

$$-V_{EE} + I_E R_E + V_{BE} = 0$$

$$I_E = \frac{V_{EE} - V_{BE}}{R_E} = 4 - 0.7/1.2 \kappa = 2.75 \text{ mA}$$

Applying KVL to the output circuit:

$$+V_{CB}+I_CR_C-V_{CC}=0$$

$$V_{CB} = V_{CC} - I_C R_C$$

with

$$I_C \cong I_F$$

$$V_{CB=} = 10 - (2.75m)(2.4k) = 3.4V$$

$I_{B=} I_{C}/\beta = 2.75 \text{ mA/60} = 45 \mu\text{A}$

Fig. 9-10

# **Example 9-5**: (Common-Collector)

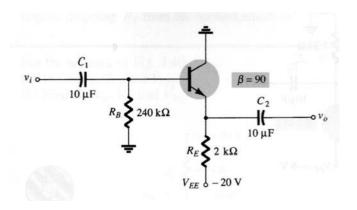

Determine  $I_E$  and  $V_{CE}$  for the common-collector (emitter-follower) configuration of Fig. 9-11.

#### Solution:

Applying KVL to the input circuit:

$$-I_{B}R_{B}-V_{BE}-I_{E}R_{E}+V_{EE}=0$$

$$I_{E} = (\beta + 1)I_{B}$$

$$I_{B} = \frac{V_{EE}-V_{BE}R_{B}}{+(\beta + 1)R_{E}}$$

$$= \frac{20-0.7}{240k+(91)(2k)} = 45.73\mu A$$

$$I_{E} = (\beta + 1)I_{B} = (91)(45.73\mu) = 4.16mA$$

Fig. 9-11

Applying KVL to the output circuit

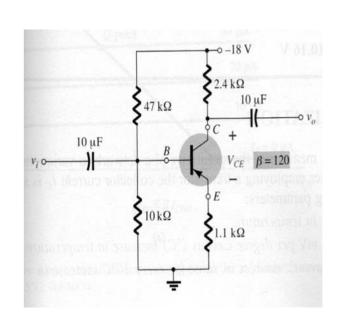

# **Example 9-6**: (PNP Transistor)

Determine  $V_{CE}$  for the voltage-divider bias configuration of Fig. 9-12.

### Solution:

Testing:

$$\beta R_E \ge 10R_2$$

$(120)(1.1k) \ge 10(10k)$

$132k\Omega \ge 100k\Omega(satisfied)$

$V_B = \frac{R_2V_{CC}}{R_1 + R_2} = \frac{(10k)(-18)}{47k + 10k}$

$= -3.16V$

$V_E = V_B - V_{BE} = -3.16 - (-0.7) = -2.46V$

$I_C = I_E = \frac{V_E}{R_E} = \frac{2.46}{1.1k} = 2.24mA$

$$-I_E R_E + V_{CE} - I_C R_C + V_{CC} = 0$$

(KVL)

$$V_{CE} = -V_{CC} + I_C (R_C + R_E)$$

$$= -18 + (2.24m)(2.4k + 1.1k) = -10.16V$$

## **Exercises:**

- 1. For the fixed-biased configuration of Fig. 9-2a with the following parameters:  $V_{CC} = +12 \text{ V}$ ,  $\beta = 50$ ,  $R_B = 240 \text{ k}\Omega$ , and  $R_C = 2.2 \text{ k}\Omega$ , determine:  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_B$ ,  $V_C$ , and  $V_{BC}$ .

- 2. For the emitter bias circuit of Fig. 9-4a with the following parameters:  $V_{CC}$  = +20 V,  $\beta$  = 50,  $R_B$  = 430 k $\Omega$ ,  $R_C$  = 2 k $\Omega$ , and  $R_E$  = 1 k $\Omega$ , determine:  $I_B$ ,  $I_C$ ,  $V_{CE}$ ,  $V_C$ ,  $V_E$ ,  $V_B$  and  $V_{BC}$ .

- 3. Determine the dc bias voltage  $V_{CE}$  and the current  $I_C$  for the voltage-divider configuration of Fig. 9-6a with the following parameters:  $V_{CC} = +18 \text{ V}$ ,  $\beta = 50, R_I = 82 \text{ k}\Omega$ ,  $R_2 = 22 \text{ k}\Omega$ ,  $R_C = 5.6 \text{ k}\Omega$ , and  $R_E = 1.2 \text{ k}\Omega$ .